老樣子從昨天寫的程式開始

程式碼如下:

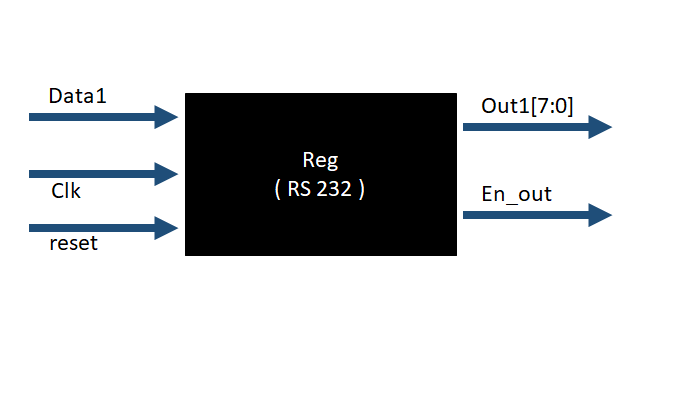

module Rs232_test1(Data1,clk,reset1,Out1,En_out);

input Data1,reset1 ,clk;

output[7:0] Out1;

output En_out;

因此我們知道

看一下圖片

因此我們定義一個 tb

module tb1();

endmodule

因此我們定義一個 tb 的 Rs232_test1 就稱呼為 Rs232_test_tb1

module tb1();

// 定義一個 tb 的 Rs232_test1 就稱呼為 Rs232_test_tb1

Rs232_test1 Rs232_test_tb1(.Data1(),.clk(),.reset1(),.Out1(),.En_out());

endmodule

現在要寫 TB 就是測試這個電路,所以首先要有3個 reg 分別是要接入 input 的訊號

為什麼要用 佔存器,因為等等會做控制

module tb1();

// 3個 reg 分別是要接入 input 的訊號

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

Rs232_test1 Rs232_test_tb1(.Data1(),.clk(),.reset1(),.Out1(),.En_out());

endmodule

接下來要收2個 Output 的訊號,所以要寫兩個 Wire 來接線

module tb1();

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

// 收2個 Output 的訊號,所以要寫兩個 Wire 來接線

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(.Data1(),.clk(),.reset1(),.Out1(),.En_out());

endmodule

將他接上

Rs232_test1 Rs232_test_tb1(.Data1(),.clk(),.reset1(),.Out1(),.En_out());

接上後

** Rs232_test1 Rs232_test_tb1( **

** .Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1), **

** .Out1(Out_tb1),.En_out(En_out_tb1)); **

module tb1();

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

// 收2個 Output 的訊號,所以要寫兩個 Wire 來接線

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(

.Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1),

.Out1(Out_tb1),.En_out(En_out_tb1)

);

endmodule

接下來開始寫 剛剛 input 的 reg 設定方法

使用 initial

module tb1();

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(

.Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1),

.Out1(Out_tb1),.En_out(En_out_tb1)

);

// 使用 initial

initial begin

end

endmodule

第一步的 tb 就是將他的 reg 初始化

initial 開頭將 input 的 reg 設定初始直

2. reg clk_tb1<=0;

3. reg reset_tb1<=0;

module tb1();

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(

.Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1),

.Out1(Out_tb1),.En_out(En_out_tb1)

);

// 使用 initial

initial begin

clk_tb1<=0; reset_tb1<=0;

end

endmodule

接下來,製作 Clk 的時間,週期為 10 個時間,所以設定為 每 5個反轉

** always #5 clk<=~clk; **

module tb1();

reg Data_tb1;

reg clk_tb1;

reg reset_tb1;

Wire[7:0] Out_tb1;

Wire En_out_tb1;

Rs232_test1 Rs232_test_tb1(

.Data1(Data_tb1),.clk(clk_tb1),.reset1(reset_tb1),

.Out1(Out_tb1),.En_out(En_out_tb1)

);

initial begin

Data_tb1<=0; clk_tb1<=0; reset_tb1<=0;

// 週期為 10 個時間,所以設定為 每 5個反轉

end

always #5 clk<=~clk;

endmodule

我們上面沒寫到 input 的 Data ,因為 Data 就是 RS232 的資料,明天再來撰寫